サマリー

前回、”コンピューターを構成する計算要素と半導体チップについて“で述べた半導体チップを設計するプロセスと、”ソフトウェア技術者のため のFPGA入門 機械学習編“から一歩進めたAIアプリケーションに特化した半導体チップについて述べたいと思う。半導体の設計技術とそれらに適用されるAI技術

前回”コンピューターを構成する計算要素と半導体チップについて“で述べた半導体チップを設計するプロセスは、以下のような一般的な手順となる。

- 要件定義(機能設計) 他のハード/ソフトウェアの製造物と同様に設計する半導体の要件を定義する。どのような機能を実現するか、どのような性能が必要かなどを明確にする。

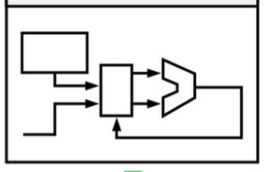

- 論理設計 “コンピューターを構成する計算要素と半導体チップについて“で述べたようにコンピューターは2値のスイッチングトランジスタを組み合わせた構造となっている。それらの構造は論理式で表され、機能ブロック(モジュール、セル)に基づいたブックを設計する。

- 回路設計 次に、論理設計をベースにトランジスタ回路(や電源、信号伝搬回路)等の回路設計を行う。回路設計では、論理回路の設計や回路図の作成などが行われる。

ここでは回路設計した回路の動作をシミュレーションするためのツールが用いられる。代表的なものに、SPICEやVerilogなどがある。

- シミュレーション 回路設計が完了したら、シミュレーションを行う。シミュレーションでは、回路が正しく動作するかどうか、性能が要件を満たしているかどうかなどを確認する。

- 物理(レイアウト)設計 シミュレーションが完了したら、物理設計を行う。物理設計では、回路の配置や配線などが行われる。この工程で、半導体のサイズや形状が決定される。

ここでは、回路の配線を設計するためのツールであるレイアウトツールが用いられる。代表的なものに、Cadence VirtuosoやSynopsys Custom Compilerなどがある。

- プロセス設計 半導体構造の主に縦方向のプロセス設計を、プロセス装置の特性と過去のプロセスデータを元に設計する。

プロセス設計時には、回路が実際に製造された際の物理的な特性をシミュレーションするためのツールが用いられる。代表的なものに、TCADやSilvacoなどがある。

- マスク作成 物理設計が完了したら、マスク作成が行われる。マスクは、半導体を製造するためのパターンを描いたものとなる。

- ウエハ製造・ デバイス製造 マスクが完成したら、ウエハ製造が行われる。ウエハ製造では、シリコンウエハ上にマスクに基づいてパターンが書き込まれ、半導体素子が形成される。さらにウエハ製造が完了したら、デバイス製造が行われる。デバイス製造では、半導体素子に電極を取り付けたり、保護層を形成したりするなどの加工が行われる。

- 評価・検査 最後に、製造された半導体の評価や検査が行われる。評価や検査では、半導体の性能や品質が規定を満たしているかどうかが確認される。

ここでは、製造された半導体デバイスの性能や品質を評価するための評価・検査ツールが用いられる。

このような半導体設計を行うにあたり様々な領域にAIが適用されている。以下にそれらの事例について述べる。

- 最適化 AIによって半導体設計の最適化を行うことができる。例えば、回路の構成やパラメータを自動的に最適化することで、消費電力の削減や高速化などが可能になる。回路シミュレーションツール、物理シミュレーションツール、レイアウトツールにはこのような最適化ツールが含まれている。

最適化を行うための技術としては、”命題論理の充足可能性判定問題(SAT:Boolean SAtisfiability)について”で述べたSATソルバーや”劣モジュラ最適化と機械学習“で述べた劣モジュラ最適化技術、さらに”深層学習について“で述べている深層学習技術、”グラフデータ処理アルゴリズムと機械学習/人工知能タスクへの応用“で述べてられているグラフデータ技術等がある。具体的にはDeep Learningを用いた回路構成最適化や、Reinforcement Learningを用いた回路最適化、メタヒューリスティック最適化の適用が現実に行われている。

具体的な例としては”深層強化学習を使って半導体チップの設計を自動化“ではチップの配置問題を深層強化学習による解決が述べられていたり、”「機械学習」が最先端半導体回路の研究を熱くする“では最先端半導体チップの研究開発成果が披露される国際学会「ISSCC(International Solid-State Circuits Conference)」にて注目されているセッションは「機械学習と信号処理」と「無線技術」とであると述べられている。

- パターンマッチング 異常検知やトラブルシューティングにおいて、異常なパターンの検出が可能になる。異常パターンを自動的に検出することで、品質管理や製造工程の改善が可能になる。パターンマッチングに用いられる技術は”深層学習について“で述べている深層学習技術、また”異常検知と変化検知技術“で述べられている変化検知技術がある。

具体的には、”半導体製造工場における Virtual Metrology 技術 “に述べられている各種計測データを統計的 手法によって処理することで現物の出来上がりを 仮想的に予測する VM(Virtual Metrology)技術、”半導体製造装置へのAIの適用“に様々な事例が述べられている。

- 予測分析 AIによって将来の半導体の性能や信頼性を予測することができる。データ分析によって、潜在的な問題や改善点を特定することができる。これらには”一般的な機械学習とデータ分析“で述べられているような統計分析・回帰分析技術等が適用される。また”統計的因果推論と探索“で述べられているような因果推論技術も適用できる。

- 自己学習 “ワークフロー&サービス技術“で述べられているようなフロー最適化の学習をすることで、設計プロセスの高度化が可能になる。例えば、従来は経験則に基づいて行われていた設計の決定を、AIが自動的に学習し、高度化することができる。

AIアプリケーション用半導体チップについて

“米中IT大手が独自の半導体チップ開発 AI時代に照準“にも述べられているように、現在米中のIT(情報技術)大手を中心に、自社の製品やサービス向けに独自設計チップを開発する動きが本格化してきている。ここではまず、それらAIアプロケーション向けの半導体設計を行う際の設計上の特徴的について述べ、さらにいくつかの具体的な事例について述べる。

まず設計上の特徴は以下のようになる。

- アーキテクチャ設計:AI用の半導体を設計するにあたって、最初に行うべきことは、AIアルゴリズムを効率的に実行するためのアーキテクチャを設計することとなる。例えば、深層学習アルゴリズムを処理するために、多数の並列演算ユニットを持つアーキテクチャが必要になる場合がある。

- 高速化:AI用の半導体は、高速である必要がある。処理速度を向上させるために、半導体のクロック周波数を増やす、または複数のコアを持つプロセッサを設計するなどの施策が必要となる。例えば、深層学習アルゴリズムを実行するためには、多数の並列演算ユニットを持つ半導体が必要になり、AIアルゴリズムの処理速度を向上させるために、半導体のクロック周波数を増やしたり、複数のコアを持つプロセッサを設計する必要がある場合もある。

- 効率性:AIアルゴリズムを実行するためには、大量のデータを処理する必要がある。そのため、半導体の消費電力を抑えることが重要となる。低消費電力の設計や、電力効率の高い演算ユニットの採用などが効果的になる。

- メモリ管理:AIアルゴリズムを実行するには、大量のデータをメモリに保存する必要がある。そのため、半導体のメモリ管理にも注意を払う必要がある。例えば、高速なメモリアクセスを可能にするために、キャッシュを使用するなどの設計がある。

- データ処理:AIアルゴリズムを実行するためには、特定のデータ型をサポートする必要がある。例えば、浮動小数点数の演算を高速に処理できるようにするなどの設計がある。

- ソフトウェアサポート:AIアルゴリズムを実行するためには、python等の特定のソフトウェアライブラリをサポートする必要がある。そのため、半導体設計においては、ソフトウェアとの互換性を考慮する必要がある。

AI用途に特化した半導体チップは、GPUやCPUなどの汎用プロセッサと比較して、高速かつ省電力な処理が可能なため、現在AI分野において大きな注目を集めている。以下にいくつかの具体例を挙げる。

- NVIDIA Tesla GPU NVIDIAのTesla GPUは、GPUの高い並列処理能力を利用して、ディープラーニングモデルのトレーニングや推論を高速かつ効率的に実行できるように設計されている。また、TensorCoreと呼ばれる特別な回路を搭載しており、浮動小数点演算を高速化することができる。

- Google TPU GoogleのTPU(Tensor Processing Unit)は、Googleが自社で開発したAI用途に特化した半導体チップとなる。TPUは、ディープラーニングの推論に特化しており、高速かつ効率的な推論を実現することができる。また、Google Cloudで提供されるクラウドサービスに組み込まれているため、簡単に利用することができる。

- Intel Nervana Neural Network Processor IntelのNervana NNPは、ニューラルネットワークのトレーニングや推論に特化した半導体チップとなる。NNPは、高速で効率的な演算を実行することができるように設計されており、ディープラーニング分野での利用が期待されている。

- Qualcomm Snapdragon Neural Processing Engine QualcommのSnapdragon Neural Processing Engineは、スマートフォンやタブレットなどのモバイルデバイス上でディープラーニングモデルを実行するための半導体チップとなる。Snapdragon NPEは、高速で効率的な演算を実行することができるため、モバイルアプリケーションやIoTデバイスなどでの利用が期待されている。

このほかにも様々な企業がAI用チップの開発を行っている。これらのAI用途に特化した半導体チップの用途としては、データをインプットする場で処理を完結するエッジコンピューティングや、従来のGPUを更に高速化する等が考えられている。

さらに最新の情報として”WordやPhotoshopにも生成AI。推論性能を強化するNVIDIAの新GPUなど、AIプロセッサ市場の競争が激化“では2022のGTC(GPU Technology Conference)にて、AI向けGPUの最新版としてHopperの開発コードネームを持つ「NVIDIA H100 GPU」が発表されている。

そして、このNVIDIA H100 GPUを8つ搭載している学習用スーパーコンピューター「DGX-H100」が2023年に出荷されている。このような高性能な学習用演算装置を用いることで、近年の学習時間がかかるモデルの計算が短縮されるものとなる。

また、NVIDIAだけではなくSambaNovaやTenstorrentなどの半導体ベンチャーが開発した、AI特化のプロセッサやアクセラレータなども注目を集めている。Intelが買収してラインナップに加えているHabana Labsのアクセラレータもここに入る。

AI専用プロセッサやアクセラレータの特徴は、電力あたりの処理能力、つまり電力効率が汎用プロセッサのGPUよりも優れていることだが、その反面独自のプログラミングモデルを学ばなければならないというのが課題になる。

さらに、エッジ側、つまりクライアントPCやスマートフォンに搭載されるNPU(Neural Processing Unit)の開発も近年活発に行われている。具体的な例としては、Qualcommのスマートフォン用SoC(Snapdragon 8 Gen 2)に内蔵されているNPU(同社の呼び方ではDSP)やApple者もスマートフォン用SoC(M1&M2チップ)にNPUを内蔵しているものを開発している。

また、x86プロセッサでも、AMDがRyzen 7000モバイルプロセッサのうち開発コードネーム「Phoenix」で呼ばれているダイに、Xilinx由来のFPGAを統合することで、NPUとして利用できるようにしている。

Intelは開発コードネームKeem Bayで知られる単体NPUをOEMメーカーに提供しており、今年後半に登場予定の次世代製品「Meteor Lake」でCPUに統合する計画となる。

なお、機械学習技術へのハードウェアアプローチに関しては”Thinking Machines 機械学習とそのハードウェア実装“や”ソフトウェア技術者のため のFPGA入門 機械学習編“にも述べている。そちらも参照のこと。

AIシステム設計・意思決定構造の設計を専門としています。

Ontology・DSL・Behavior Treeによる判断の外部化、マルチエージェント構築に取り組んでいます。

Specialized in AI system design and decision-making architecture.

Focused on externalizing decision logic using Ontology, DSL, and Behavior Trees, and building multi-agent systems.